TSMC planeja superprocessadores de 1000W com desempenho 40 vezes maior que modelos atuais

A TSMC está preparando uma nova revolução no mercado de chips para Data Centers e aplicações de IA. A empresa anunciou, durante seu Simpósio de Tecnologia da América do Norte, que está desenvolvendo uma nova geração de pacotes multi-chiplet que poderão atingir incríveis 1000W de consumo, abrigando interposers com área até 9,5 vezes maior que os atuais limites de fotomáscara.

Com substratos de até 120×150 mm (18.000 mm²) — quase o tamanho de uma caixa de CD — a tecnologia poderá suportar até 40 vezes mais desempenho do que os chips convencionais, posicionando a empresa de maior fundição de semicondutores do mundo como referência em empacotamento avançado para computação de alto desempenho.

Escalando os limites do empacotamento

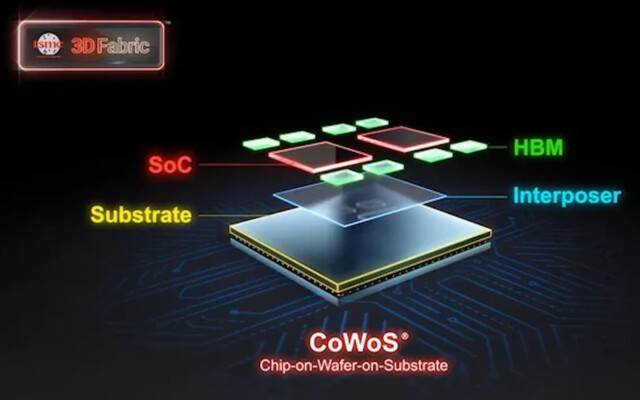

Atualmente, a tecnologia CoWoS da TSMC já permite interposers de até 2831 mm², utilizados por gigantes como AMD (Instinct MI300X) e NVIDIA (B200), que combinam múltiplos chiplets lógicos com pilhas de memória HBM3.

No entanto, a demanda crescente por mais potência computacional fez com que a empresa traçasse um novo plano: o 3DFabric Roadmap, que visa ampliar significativamente as dimensões dos interposers.

O próximo passo será a chegada da tecnologia CoWoS-L de nova geração, com interposers de até 4719 mm² e suporte para 12 pilhas de HBM, montados sobre substratos de 100×100 mm (10.000 mm²). Essa fase já deverá oferecer 3,5 vezes mais desempenho que os designs atuais.

Para clientes que exigem desempenho extremo e estão dispostos a pagar por isso, oferecemos tecnologias como o SoW-X, com integração em nível de wafer

Próxima fronteira: chiplets empilhados e wafer-level integration

A etapa seguinte, voltada para aplicações ainda mais exigentes, incluirá assemblies 3D com até quatro sistemas empilhados (SoIC) — combinando nós como N2/A16 sobre chips N3 —, 12 pilhas de HBM4 e dies de I/O dedicados, tudo isso montado sobre um interposer de 7885 mm², o maior já planejado pela empresa.

Para clientes de nicho, como Cerebras e Tesla, a TSMC também aposta na abordagem System-on-Wafer (SoW-X), onde todo o sistema é construído em um wafer completo, eliminando os limites físicos dos pacotes convencionais.

Entrega de energia: o próximo desafio dos chips de kilowatt

Alimentar esses monstros computacionais com energia suficiente é um dos maiores desafios da indústria. A TSMC pretende resolver isso integrando circuitos de gerenciamento de energia (PMICs) baseados em sua tecnologia N16 FinFET diretamente nos interposers com RDL (Redistribution Layers).

Com a ajuda de TSVs (vias verticais) e indutores no próprio wafer, será possível entregar corrente com eficiência e reduzir perdas de resistência parasita.

Além disso, os pacotes contarão com capacitores embutidos (eDTCs) com densidade de até 2500 nF/mm², responsáveis por suavizar variações de tensão e manter a estabilidade do sistema mesmo sob cargas de trabalho intensas e dinâmicas.

Leia também:

- TSMC diz que não tem controle sobre onde vão parar os chips que fabrica

- TSMC nega que estaria formando uma joint venture com a Intel

- NVIDIA e parceiras pretendem investir US$ 500 bilhões em servidores de IA nos EUA

Impacto no design e na refrigeração

Esses superchips exigem muito mais do que apenas avanços em empacotamento e energia. O tamanho dos substratos propostos ultrapassa os limites do atual padrão OAM 2.0, que mede 102×165 mm. Isso indica que novos formatos de módulos e placas-mãe precisarão ser desenvolvidos.

Em termos de refrigeração, soluções tradicionais não serão suficientes. Fabricantes de hardware já estão testando refrigeração líquida direta e imersão total, tecnologias cruciais para lidar com os níveis de calor gerados por chips de múltiplos kilowatts. A própria NVIDIA já adota essas técnicas em seus designs NVL72 com GPUs GB200/300.

Fonte: TSMC